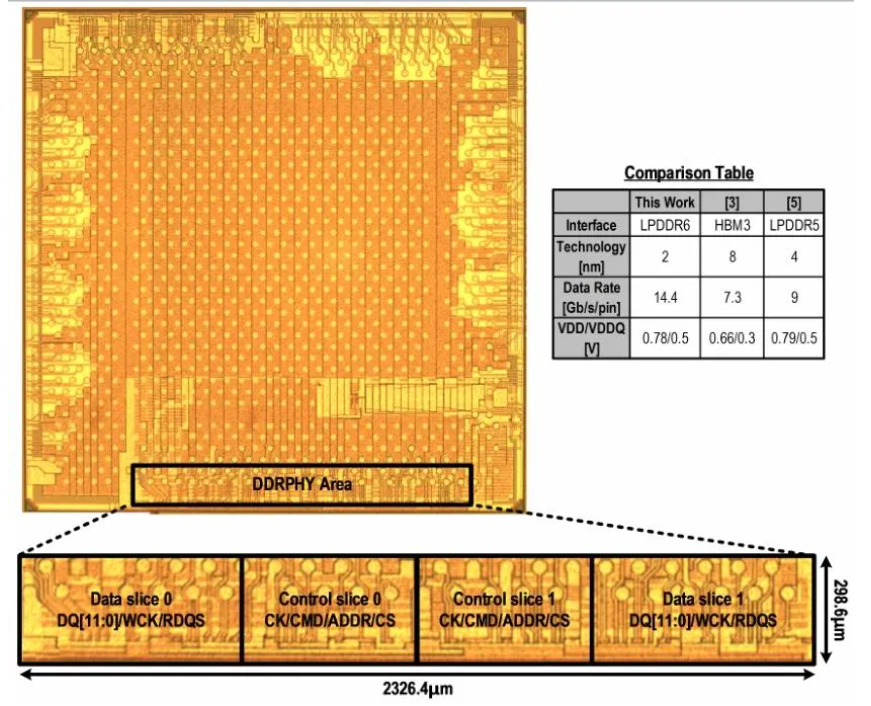

在 2026 年 IEEE 国际固态电路会议(ISSCC)上,三星电子展示了内存接口领域的里程碑式成果:全球首款基于 2nm MBCFET 工艺的全数字 LPDDR6 物理层(PHY) 芯片。该芯片不仅跑出了 14.4Gb/s 的引脚速率极限,更通过四大技术创新,将功耗最高降低了 59%。

一、 行业背景:AI 时代的“带宽与能效”双重焦虑

随着端侧 AI(On-device AI)、8K 视频和沉浸式 AR 应用的爆发,LPDDR 接口面临着前所未有的挑战。传统 PHY 设计在迈向 LPDDR6 时代时,撞上了三面“墙”:

时钟功耗墙: 频率翻倍导致时钟缓冲器功耗失控。

时序墙: 传统 DFE(判决反馈均衡器)在超高速下难以满足 1UI 的反馈约束。

能效墙: 传统设计在中低频场景(DVFS)下存在巨大的功耗冗余。

二、 2nm MBCFET:不仅仅是工艺的胜利

三星此次采用了尖端的 2nm MBCFET(多桥通道场效应管) 工艺。相比传统的 FinFET,MBCFET 的环绕栅极(GAA)结构提供了更强的静电控制能力和更高的驱动电流,这为全数字电路在低电压(0.78V)下稳定运行提供了物理基础。

三、 四大核心技术创新:全链路重塑 PHY 架构

1. 四分之一速率时钟 + QEC 校准

痛点: 高频时钟会导致严重的信号抖动和功耗。 突破: 三星采用了四分之一速率正交时钟架构,通过降低主频来抑制抖动。同时,首创 正交误差校正(QEC)训练机制,利用数字延迟线实现亚 LSB 级的相位微调。

成果: 12.2Gb/s 下写窗口裕量提升 41.6%,彻底解决了四相时钟失配问题。

2. 多级 FIFO 预测式 DFE

痛点: 14.4Gb/s 速率下,标准单元的逻辑延迟远超 1UI,传统 DFE 无法及时反馈。 突破: 引入多级 FIFO 预测式架构,通过“零周期读取”方法拉平时序路径。

成果: 成功绕过了反馈循环中的多路选择器延迟,让 PHY 在标准单元库下也能稳跑 14.4Gb/s。

3. 基于相位计数器的可重配置串行器

痛点: LPDDR6 需兼容 1:6 和 1:8 两种 DFI 规范,传统方案需要两套冗余硬件。 突破: 三星设计了一套可重配置串行器,通过相位计数器动态切换 12:1 或 16:1 模式。

成果: 以极小的硬件开销实现了高总线效率与向后兼容性的完美平衡。

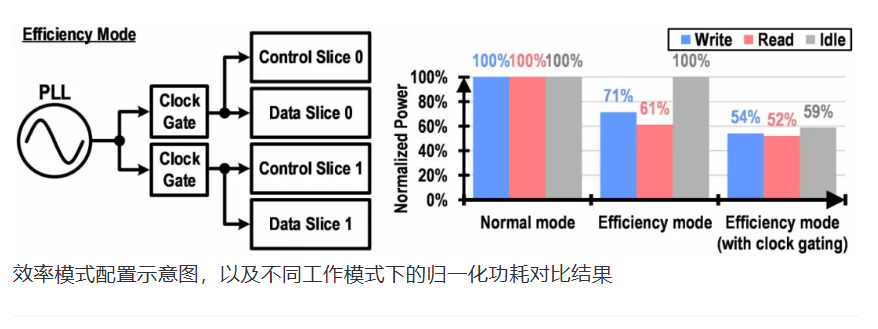

4. 深度时钟门控(Clock Gating)

痛点: 即使在 LPDDR6 的“效率模式”下,PHY 侧的时钟树依然在空转耗电。 突破: 新增 PHY 侧深度时钟门控技术,在副子通道闲置时,彻底切断时钟缓冲器树的翻转。

成果: 相比原生模式,写/读/空闲功耗分别进一步降低了 46% / 48% / 59%。

四、 实测表现:量产级的稳健性

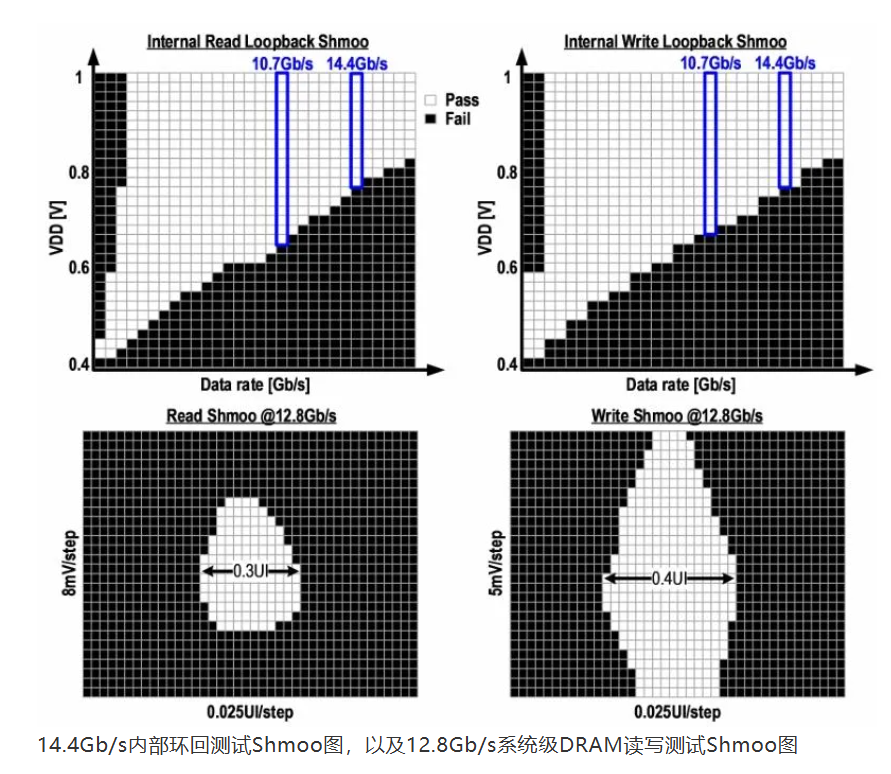

在三星 2nm 工艺的加持下,该芯片表现惊人:

电压性能: 在 0.78V 工作电压下,内部环回测试稳定达到 14.4Gb/s。

系统验证: 搭配商用 LPDDR6 DRAM 联调,12.8Gb/s 下读写窗口裕量保持在 0.3UI - 0.4UI,展示了极高的商业化成熟度。

五、 总结:端侧 AI 的新基石

三星这款全数字 LPDDR6 PHY 的发布,标志着接口设计从“模拟主导”全面转向“数字智能”。它不仅解决了 LPDDR6 标准下的速率瓶颈,更通过极致的功耗控制,为下一代旗舰手机和 AI 芯片提供了核心推力。

专家点评: “三星通过工艺(2nm)与算法(QEC/FIFO DFE)的双重降维打击,证明了全数字 PHY 才是未来移动 SoC 的终极形态。”

评论区